## ARM7TDMI Microprocessor Core

### **Technical Manual**

November 1998

Order Number C14060

This document contains proprietary information of LSI Logic Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of an officer of LSI Logic Corporation.

Document DB14-000058-02, First Edition (November 1998) This document describes revision A of LSI Logic Corporation's ARM7 TDMI Microprocessor and will remain the official reference source for all revisions of this product until rescinded by an update.

### To receive product literature, call us at 1.800.574.4286 (U.S. and Canada); +32.11.300.531 (Europe); 408.433.7700 (outside U.S., Canada, and Europe) and ask for Department JDS; or visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 1996–1998 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

The LSI Logic logo design, CoreWare, Gigablaze, and G10 are registered trademarks and FlexStream, and Right-First-Time are trademarks of LSI Logic Corporation. ARM is a registered trademark, the ARM Powered logo, and ICEBreaker are trademarks of Advanced RISC Machines Ltd., used under license. All other brand and product names may be trademarks of their respective companies.

### Contents

| Preface   |                     |                                           |      |  |  |

|-----------|---------------------|-------------------------------------------|------|--|--|

| Chapter 1 | Intro               | duction                                   |      |  |  |

|           | 1.1                 | Introduction                              | 1-1  |  |  |

|           |                     | 1.1.1 General Information                 | 1-1  |  |  |

|           |                     | 1.1.2 LSI Logic's ARM7TDMI Implementation | 1-2  |  |  |

|           | 1.2                 | ARM7TDMI Architecture                     | 1-2  |  |  |

|           |                     | 1.2.1 The THUMB Concept                   | 1-3  |  |  |

|           |                     | 1.2.2 THUMB Advantages                    | 1-3  |  |  |

|           | 1.3                 | CoreWare <sup>®</sup> Program             | 1-6  |  |  |

| Chapter 2 | Signal Descriptions |                                           |      |  |  |

|           | 2.1                 | Core Logic Diagram                        | 2-1  |  |  |

|           | 2.2                 | Clock Signals                             | 2-3  |  |  |

|           | 2.3                 | Interrupt Signals                         | 2-3  |  |  |

|           | 2.4                 | Bus Control Interface                     | 2-4  |  |  |

|           | 2.5                 | Debug Interface                           | 2-7  |  |  |

|           | 2.6                 | Boundary Scan Control Interface           | 2-9  |  |  |

|           | 2.7                 | Boundary Scan Interface                   | 2-11 |  |  |

|           | 2.8                 | Processor Interface                       | 2-12 |  |  |

|           | 2.9                 | Memory Interface                          | 2-12 |  |  |

|           | 2.10                | Coprocessor Interface                     | 2-15 |  |  |

|           | 2.11                | Test Signals                              | 2-16 |  |  |

| Chapter 3 | Prog | rammer'  | s Model                                 |      |

|-----------|------|----------|-----------------------------------------|------|

|           | 3.1  | Proces   | sor Operating States                    | 3-1  |

|           | 3.2  | Switchi  | ng State                                | 3-2  |

|           |      | 3.2.1    | Entering THUMB State                    | 3-2  |

|           |      | 3.2.2    | Entering ARM State                      | 3-2  |

|           | 3.3  | Memor    | y Formats                               | 3-2  |

|           |      | 3.3.1    | Big Endian Format                       | 3-2  |

|           |      | 3.3.2    | Little Endian Format                    | 3-3  |

|           | 3.4  | Instruct | tion Length                             | 3-3  |

|           | 3.5  | Data Ty  | ypes                                    | 3-4  |

|           | 3.6  | Operat   | ing Modes                               | 3-4  |

|           | 3.7  | Registe  | ers                                     | 3-4  |

|           |      | 3.7.1    | The ARM State Register Set              | 3-5  |

|           |      | 3.7.2    | The THUMB State Register Set            | 3-6  |

|           |      | 3.7.3    | The Relationship Between ARM and THUMB  |      |

|           |      |          | State Registers                         | 3-7  |

|           |      | 3.7.4    | Accessing High Registers in THUMB State | 3-8  |

|           | 3.8  | Progra   | m Status Registers                      | 3-9  |

|           |      | 3.8.1    | The Condition Code Flags                | 3-9  |

|           |      | 3.8.2    | Reserved Bits                           | 3-10 |

|           |      | 3.8.3    | The Control Bits                        | 3-10 |

|           | 3.9  | Except   | ions                                    | 3-11 |

|           |      | 3.9.1    | Action on Entering an Exception         | 3-11 |

|           |      | 3.9.2    | Action on Leaving an Exception          | 3-12 |

|           |      | 3.9.3    | Exception Entry/Exit Summary            | 3-13 |

|           |      | 3.9.4    | Fast Interrupt Request (FIQ)            | 3-13 |

|           |      | 3.9.5    | Interrupt Request (IRQ)                 | 3-14 |

|           |      | 3.9.6    | Abort                                   | 3-14 |

|           |      | 3.9.7    | Software Interrupt (SWI)                | 3-15 |

|           |      | 3.9.8    | Undefined Instruction (UDEF)            | 3-16 |

|           |      | 3.9.9    | Exception Vectors                       | 3-16 |

|           |      | 3.9.10   | Exception Priorities                    | 3-16 |

|           | 3.10 | Interrup | ot Latencies                            | 3-17 |

|           | 3.11 | Reset    |                                         | 3-18 |

|           | 3.12 | Pipelin  | e Architecture                          | 3-18 |

| Chapter 4 | ARM  | Instructi | on Set Summary                                     |        |

|-----------|------|-----------|----------------------------------------------------|--------|

|           | 4.1  | Instructi | on Set Summary                                     | 4-1    |

|           | 4.2  | Format    | Summary                                            | 4-3    |

|           | 4.3  | Instructi | on Condition Field                                 | 4-4    |

|           | 4.4  | Instructi | on Set Examples                                    | 4-5    |

|           |      | 4.4.1     | Using the Conditional Instructions                 | 4-6    |

|           |      | 4.4.2     | Pseudo-Random Binary Sequence Generator            | 4-8    |

|           |      | 4.4.3     | Multiplication by Constant Using the Barrel Shifte | er 4-8 |

|           |      | 4.4.4     | Loading a Word from an Unknown Alignment           | 4-10   |

| Chapter 5 | THU  | MB Instru | iction Set Summary                                 |        |

|           | 5.1  | Instructi | on Set Summary                                     | 5-1    |

|           |      | 5.1.1     | Instruction Cycle Time                             | 5-3    |

|           | 5.2  | Format    | Summary                                            | 5-3    |

|           | 5.3  | Instructi | on Set Examples                                    | 5-4    |

|           |      | 5.3.1     | Multiplication by a Constant Using Shifts and Add  | ds 5-4 |

|           |      | 5.3.2     | General Purpose Signed Divide                      | 5-5    |

|           |      | 5.3.3     | Division by a Constant                             | 5-8    |

| Chapter 6 | Mem  | ory Inter | ace                                                |        |

|           | 6.1  | Overvie   | W                                                  | 6-1    |

|           | 6.2  | Cycle T   | /pes                                               | 6-2    |

|           | 6.3  | Address   | ; Timing                                           | 6-4    |

|           | 6.4  | Data Tra  | ansfer Size                                        | 6-7    |

|           | 6.5  | Instructi | on Fetch                                           | 6-8    |

|           | 6.6  | Memory    | Management                                         | 6-10   |

|           | 6.7  | Locked    | Operations                                         | 6-10   |

|           | 6.8  | Stretchi  | ng Access Times                                    | 6-11   |

|           | 6.9  | ARM7T     | DMI Data Bus                                       | 6-11   |

|           | 6.10 | Externa   | l Data Bus                                         | 6-13   |

|           |      | 6.10.1    | The Unidirectional Data Bus                        | 6-14   |

|           |      | 6.10.2    | Bidirectional Data Bus                             | 6-15   |

|           |      | 6.10.3    | Example System: The ARM7TDMI Test Chip             | 6-18   |

| Chapter 7 | Сор | rocessor   | Interface                  |      |

|-----------|-----|------------|----------------------------|------|

|           | 7.1 | Overvie    | W                          | 7-1  |

|           | 7.2 | Interfac   | e Signals                  | 7-1  |

|           |     | 7.2.1      | Coprocessor Present/Absent | 7-2  |

|           |     | 7.2.2      | Busy (Waiting)             | 7-2  |

|           |     | 7.2.3      | Pipeline Following         | 7-3  |

|           |     | 7.2.4      | Data Transfer Cycles       | 7-3  |

|           | 7.3 | Registe    | er Transfer Cycle          | 7-3  |

|           | 7.4 | Privileg   | ed Instructions            | 7-4  |

|           | 7.5 | Idempo     | otency                     | 7-4  |

|           | 7.6 | Undefir    | ned Instructions           | 7-5  |

| Chapter 8 | Deb | ug Interfa | ace                        |      |

|           | 8.1 | Overvie    | 9W                         | 8-1  |

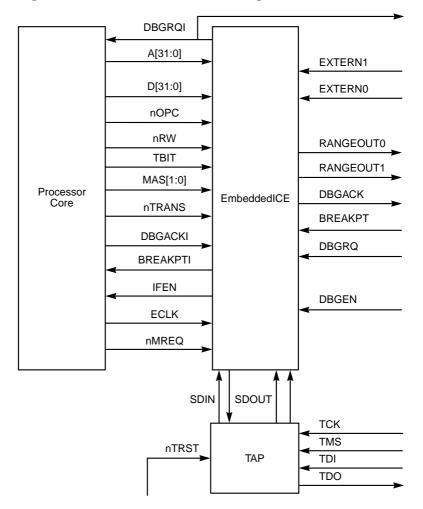

|           | 8.2 | Debug      | Systems                    | 8-2  |

|           | 8.3 | Debug      | Interface Signals          | 8-4  |

|           |     | 8.3.1      | Entry into Debug State     | 8-4  |

|           | 8.4 | Scan C     | Chains and JTAG Interface  | 8-7  |

|           |     | 8.4.1      | Scan Limitations           | 8-8  |

|           |     | 8.4.2      | The JTAG State Machine     | 8-9  |

|           | 8.5 | Reset      |                            | 8-11 |

|           | 8.6 | Pull-up    | Resistors                  | 8-11 |

|           | 8.7 | Instruct   | tion Register              | 8-11 |

|           | 8.8 | Public     | Instructions               | 8-12 |

|           |     | 8.8.1      | EXTEST (0b0000)            | 8-12 |

|           |     | 8.8.2      | SCAN_N (0b0010)            | 8-13 |

|           |     | 8.8.3      | INTEST (0b1100)            | 8-13 |

|           |     | 8.8.4      | IDCODE (0b1110)            | 8-14 |

|           |     | 8.8.5      | BYPASS (0b1111)            | 8-14 |

|           |     | 8.8.6      | CLAMP (0b0101)             | 8-14 |

|           |     | 8.8.7      | HIGHZ (0b0111)             | 8-15 |

|           |     | 8.8.8      | CLAMPZ (0b1001)            | 8-15 |

|           |     | 8.8.9      | SAMPLE/PRELOAD (0b0011)    | 8-16 |

|           |     | 8.8.10     | RESTART (0b0100)           | 8-16 |

|           | 8.9  | Test Da   | ta Registers                                 | 8-16 |

|-----------|------|-----------|----------------------------------------------|------|

|           |      | 8.9.1     | Bypass Register                              | 8-16 |

|           |      | 8.9.2     | ARM7TDMI Device Identification (ID) Code     |      |

|           |      |           | Register                                     | 8-16 |

|           |      | 8.9.3     | Instruction Register                         | 8-17 |

|           |      | 8.9.4     | Scan Chain Select Register                   | 8-18 |

|           |      | 8.9.5     | Scan Chains 0, 1, and 2                      | 8-19 |

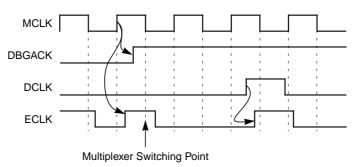

|           | 8.10 | ARM7T     | DMI Core Clocks                              | 8-24 |

|           |      | 8.10.1    | Clock Switch During Debug                    | 8-24 |

|           | 8.11 | Determ    | ining the Core and System State              | 8-25 |

|           |      | 8.11.1    | Determining the Core's State                 | 8-25 |

|           |      | 8.11.2    | Determining System State                     | 8-27 |

|           |      | 8.11.3    | Exit from Debug State                        | 8-28 |

|           | 8.12 | PC Beh    | avior During Debug                           | 8-30 |

|           |      | 8.12.1    | Breakpoint                                   | 8-30 |

|           |      | 8.12.2    | Watchpoints                                  | 8-30 |

|           |      | 8.12.3    | Watchpoint with Another Exception            | 8-31 |

|           |      | 8.12.4    | Debug Request                                | 8-31 |

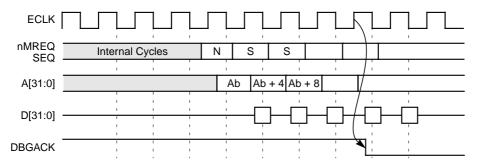

|           |      | 8.12.5    | System Speed Access                          | 8-32 |

|           |      | 8.12.6    | Summary of Return Address Calculations       | 8-32 |

|           | 8.13 | Prioritie | s/Exceptions                                 | 8-33 |

|           |      | 8.13.1    | Breakpoint with Prefetch Abort               | 8-33 |

|           |      | 8.13.2    | Interrupts                                   | 8-33 |

|           |      | 8.13.3    | Data Aborts                                  | 8-34 |

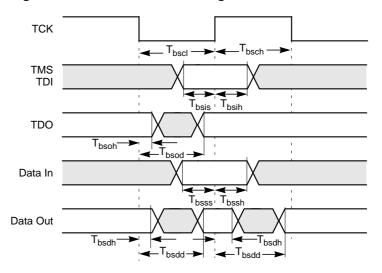

|           | 8.14 | Scan In   | terface Timing                               | 8-34 |

|           | 8.15 | Debug     | Timing                                       | 8-38 |

| Chapter 9 | Embe | eddedICI  | E Macrocell                                  |      |

|           | 9.1  | Overvie   | W                                            | 9-1  |

|           | 9.2  | Watchp    | oint Registers                               | 9-3  |

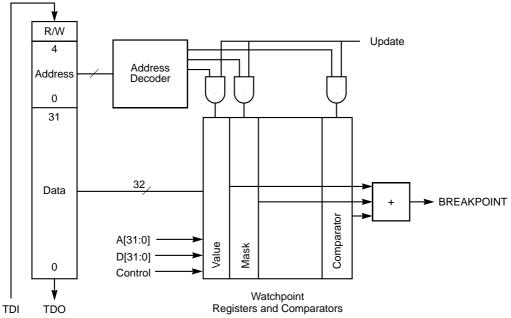

|           |      | 9.2.1     | Programming and Reading Watchpoint Registers | 9-4  |

|           |      | 9.2.2     | Using the Mask Registers                     | 9-5  |

|           |      | 9.2.3     | Control Registers                            | 9-6  |

|           | 9.3  | Program   | nming Breakpoints                            | 9-8  |

|           |      | 9.3.1     | Hardware Breakpoints                         | 9-8  |

|           |      | 9.3.2     | Software Breakpoints                         | 9-9  |

|           | 9.4  | Program   | nming Watchpoints                            | 9-10 |

|           |      |           |                                              |      |

| 9.7       Coupling Breakpoints and Watchpoints       9         9.7.1       CHAINOUT Signal       9         9.7.2       RANGEOUT Signal       9         9.8       Disabling EmbeddedICE Macrocell       9         9.9       EmbeddedICE Macrocell Timing       9         9.10       Programming Restriction       9         9.11       Debug Communication Channel       9         9.11.1       Debug Communications Control Registers       9         9.11.2       Communication Through the Communications Channel       9         9.11.2       Communication Through the Communications Channel       9         Chapter 10         Instruction Cycle Operations         10.1       Introduction       1         10.2       Branch and Branch with Link       1         10.3       THUMB Branch with Link       1         10.4       Branch and Exchange (BX)       1         10.5       Data Operations       1         10.6       Multiply and Multiply Accumulate       1         10.7       Load Register       10         10.8       Store Registers       10         10.9       Load Multiple Registers       10         10.10                                                                                                                                                     |            | 9.5    | Debug Control Register                                |       |  |

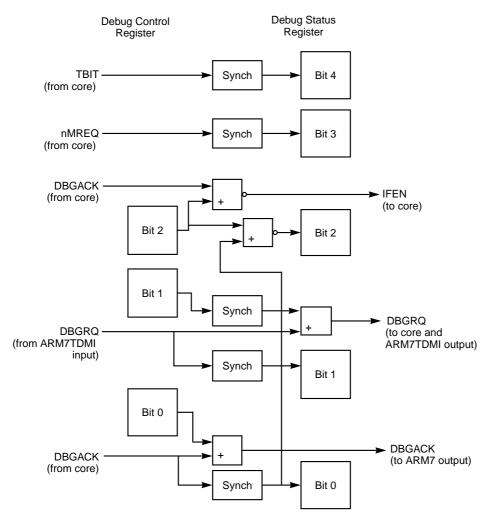

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|-------------------------------------------------------|-------|--|

| 9.7.1       CHAINOUT Signal       9         9.7.2       RANGEOUT Signal       9         9.8       Disabling EmbeddedICE Macrocell       9         9.9       EmbeddedICE Macrocell Timing       9         9.10       Programming Restriction       9         9.11       Debug Communication Channel       9         9.11       Debug Communication S Control Registers       9         9.11.2       Communication Through the Communications Channel       9         9.11.2       Communication Through the Communications Channel       9         9.11.2       Communication Through the Communications Channel       9         Chapter 10         Instruction Cycle Operations         10.1       Introduction       1         10.2       Branch and Branch with Link       1         10.3       THUMB Branch with Link       1         10.4       Branch and Exchange (BX)       1         10.5       Data Operations       1         10.6       Multiply and Multiply Accumulate       1         10.7       Load Register       10         10.8       Store Registers       10         10.10       Data Swap       10         10.11                                                                                                                                                    |            | 9.6    | Debug Status Register                                 | 9-12  |  |

| 9.7.2       RANGEOUT Signal       9         9.8       Disabling EmbeddedICE Macrocell       9         9.9       EmbeddedICE Macrocell Timing       9         9.10       Programming Restriction       9         9.11       Debug Communication Channel       9         9.11       Debug Communications Control Registers       9         9.11.1       Debug Communications Control Registers       9         9.11.2       Communication Through the Communications Channel       9         9.11       Instruction Cycle Operations       1         10.2       Branch and Branch with Link       1         10.3       THUMB Branch with Link       1         10.4       Branch and Exchange (BX)       1         10.5       Data Operations       1                                                    |            | 9.7    | Coupling Breakpoints and Watchpoints                  | 9-14  |  |

| 9.8       Disabling EmbeddedICE Macrocell       9         9.9       EmbeddedICE Macrocell Timing       9         9.10       Programming Restriction       9         9.11       Debug Communication Channel       9         9.11       Debug Communication Scontrol Registers       9         9.11.1       Debug Communications Control Registers       9         9.11.2       Communication Through the Communications       9         Chapter 10       Instruction Cycle Operations       1         10.1       Introduction       1         10.2       Branch and Branch with Link       1         10.3       THUMB Branch with Link       1         10.4       Branch and Exchange (BX)       1         10.5       Data Operations       1         10.6       Multiply and Multiply Accumulate       1         10.7       Load Register       10         10.8       Store Register       10         10.9       Load Multiple Registers       10         10.10       Store Multiple Registers       10         10.11       Data Swap       10         10.12       Software Interrupt and Exception Entry       10         10.13       Coprocessor Data Transfer (Memo                                                                                                                    |            |        | 9.7.1 CHAINOUT Signal                                 | 9-15  |  |

| 9.9       EmbeddedICE Macrocell Timing       9         9.10       Programming Restriction       9         9.11       Debug Communication Channel       9         9.11       Debug Communication Scontrol Registers       9         9.11.2       Communication Through the Communications       9         Chapter 10         Instruction Cycle Operations         10.1       Introduction       1         10.2       Branch and Branch with Link       1         10.3       THUMB Branch with Link       1         10.4       Branch and Exchange (BX)       1         10.5       Data Operations       1         10.6       Multiply and Multiply Accumulate       1         10.7       Load Register       10         10.8       Store Register       10         10.9       Load Multiple Registers       10         10.10       Store Multiple Registers       10         10.11       Data Swap       10         10.12       Software Interrupt and Exception Entry       10         10.13       Coprocessor Data Transfer (Memory to Coprocessor)       10         10.14       Coprocessor Register Transfer (Store to Coprocessor)       10                                                                                                                                           |            |        | 9.7.2 RANGEOUT Signal                                 | 9-16  |  |

| 9.10       Programming Restriction       9         9.11       Debug Communication Channel       9         9.11.1       Debug Communications Control Registers       9         9.11.2       Communication Through the Communications<br>Channel       9         Chapter 10         Instruction Cycle Operations         10.1       Introduction       1         10.2       Branch and Branch with Link       1         10.3       THUMB Branch with Link       1         10.4       Branch and Exchange (BX)       1         10.5       Data Operations       1         10.6       Multiply and Multiply Accumulate       1         10.7       Load Register       10         10.8       Store Register       10         10.9       Load Multiple Registers       10         10.11       Data Swap       10         10.12       Software Interrupt and Exception Entry       10         10.13       Coprocessor Data Operation       10         10.14       Coprocessor Data Transfer (Memory to Coprocessor)       10         10.13       Coprocessor Register Transfer (Load from Coprocessor)       10         10.16       Coprocessor Register Transfer (Load from Coprocessor) <th></th> <th>9.8</th> <th>Disabling EmbeddedICE Macrocell</th> <th>9-17</th>                          |            | 9.8    | Disabling EmbeddedICE Macrocell                       | 9-17  |  |

| 9.11       Debug Communication Channel       9         9.11.1       Debug Communications Control Registers       9         9.11.2       Communication Through the Communications<br>Channel       9         Chapter 10         Instruction Cycle Operations         10.1       Introduction       1         10.2       Branch and Branch with Link       1         10.3       THUMB Branch with Link       1         10.4       Branch and Exchange (BX)       1         10.5       Data Operations       1         10.6       Multiply and Multiply Accumulate       1         10.7       Load Register       10         10.8       Store Register       10         10.9       Load Multiple Registers       10         10.10       Store Multiple Registers       10         10.11       Data Swap       10         10.12       Software Interrupt and Exception Entry       10         10.13       Coprocessor Data Transfer (Memory to Coprocessor)       10         10.15       Coprocessor Register Transfer (Load from Coprocessor)       10         10.16       Coprocessor Register Transfer (Load from Coprocessor)       10         10.16       Coprocessor Register Trans                                                                                                     |            | 9.9    | EmbeddedICE Macrocell Timing                          | 9-17  |  |

| 9.11.1       Debug Communications Control Registers       9         9.11.2       Communication Through the Communications Channel       9         Chapter 10       Instruction Cycle Operations         10.1       Introduction       1         10.2       Branch and Branch with Link       1         10.3       THUMB Branch with Link       1         10.4       Branch and Exchange (BX)       1         10.5       Data Operations       1         10.6       Multiply and Multiply Accumulate       1         10.7       Load Register       10         10.8       Store Registers       10         10.9       Load Multiple Registers       10         10.10       Store Multiple Registers       10         10.11       Data Swap       10         10.12       Software Interrupt and Exception Entry       10         10.13       Coprocessor Data Transfer (Memory to Coprocessor)       10         10.14       Coprocessor Register Transfer (Load from Coprocessor)       10         10.16       Coprocessor Register Transfer (Store to Coprocessor)       10         10.17       Coprocessor Register Transfer (Store to Coprocessor)       10         10.18       Undefined Instructions and Cop                                                                           |            | 9.10   | Programming Restriction                               | 9-17  |  |

| 9.11.2       Communication Through the Communications<br>Channel       9         Chapter 10       Instruction Cycle Operations       1         10.1       Introduction       1         10.2       Branch and Branch with Link       1         10.3       THUMB Branch with Link       1         10.4       Branch and Exchange (BX)       1         10.5       Data Operations       1         10.6       Multiply and Multiply Accumulate       1         10.7       Load Register       10         10.8       Store Registers       10         10.10       Store Multiple Registers       10         10.11       Data Swap       10         10.12       Software Interrupt and Exception Entry       10         10.13       Coprocessor Data Transfer (Memory to Coprocessor)       10         10.14       Coprocessor Data Transfer (from Coprocessor)       10         10.15       Coprocessor Register Transfer (Load from Coprocessor)       10         10.17       Coprocessor Register Transfer (Store to Coprocessor)       10         10.18       Undefined Instructions and Coprocessor Absent       10         10.19       Unexecuted Instructions       10                                                                                                                   |            | 9.11   | Debug Communication Channel                           | 9-18  |  |

| Channel       9         Chapter 10       Instruction Cycle Operations         10.1       Introduction       1         10.2       Branch and Branch with Link       1         10.3       THUMB Branch with Link       1         10.4       Branch and Exchange (BX)       1         10.5       Data Operations       1         10.6       Multiply and Multiply Accumulate       1         10.7       Load Register       10         10.8       Store Register       10         10.9       Load Multiple Registers       10         10.10       Store Multiple Registers       10         10.11       Data Swap       10         10.12       Software Interrupt and Exception Entry       10         10.13       Coprocessor Data Operation       10         10.14       Coprocessor Data Transfer (Memory to Coprocessor)       10         10.15       Coprocessor Register Transfer (Load from Coprocessor)       10         10.16       Coprocessor Register Transfer (Store to Coprocessor)       10         10.17       Coprocessor Register Transfer (Store to Coprocessor)       10         10.18       Undefined Instructions and Coprocessor Absent       10         10.19 <td< th=""><th></th><th></th><th>9.11.1 Debug Communications Control Registers</th><th>9-18</th></td<> |            |        | 9.11.1 Debug Communications Control Registers         | 9-18  |  |

| Chapter 10       Instruction Cycle Operations         10.1       Introduction       1         10.2       Branch and Branch with Link       1         10.3       THUMB Branch with Link       1         10.4       Branch and Exchange (BX)       1         10.5       Data Operations       1         10.6       Multiply and Multiply Accumulate       1         10.7       Load Register       10         10.8       Store Register       10         10.9       Load Multiple Registers       10         10.11       Data Swap       10         10.12       Software Interrupt and Exception Entry       10         10.13       Coprocessor Data Transfer (Memory to Coprocessor)       10         10.14       Coprocessor Register Transfer (Load from Coprocessor)       10         10.16       Coprocessor Register Transfer (Store to Coprocessor)       10         10.17       Coprocessor Register Transfer (Store to Coprocessor)       10         10.18       Undefined Instructions and Coprocessor Absent       10         10.19       Unexecuted Instructions       10                                                                                                                                                                                                       |            |        | 9.11.2 Communication Through the Communications       |       |  |

| 10.1Introduction110.2Branch and Branch with Link110.3THUMB Branch with Link110.4Branch and Exchange (BX)110.5Data Operations110.6Multiply and Multiply Accumulate110.7Load Register110.8Store Register1010.9Load Multiple Registers1010.10Store Multiple Registers1010.11Data Swap1010.12Software Interrupt and Exception Entry1010.13Coprocessor Data Operation1010.14Coprocessor Data Transfer (Memory to Coprocessor)1010.15Coprocessor Register Transfer (Load from Coprocessor)1010.16Coprocessor Register Transfer (Store to Coprocessor)1010.17Coprocessor Register Transfer (Store to Coprocessor)1010.18Undefined Instructions and Coprocessor Absent1010.19Unexecuted Instructions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |        | Channel                                               | 9-19  |  |

| 10.2Branch and Branch with Link110.3THUMB Branch with Link110.4Branch and Exchange (BX)110.5Data Operations110.6Multiply and Multiply Accumulate110.7Load Register110.8Store Register1010.9Load Multiple Registers1010.10Store Multiple Registers1010.11Data Swap1010.12Software Interrupt and Exception Entry1010.13Coprocessor Data Transfer (Memory to Coprocessor)1010.14Coprocessor Data Transfer (from Coprocessor)1010.15Coprocessor Register Transfer (Load from Coprocessor)1010.17Coprocessor Register Transfer (Store to Coprocessor)1010.18Undefined Instructions and Coprocessor Absent1010.19Unexecuted Instructions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Chapter 10 | Instru | iction Cycle Operations                               |       |  |

| 10.3THUMB Branch with Link110.4Branch and Exchange (BX)110.5Data Operations110.6Multiply and Multiply Accumulate110.7Load Register110.8Store Register1010.9Load Multiple Registers1010.10Store Multiple Registers1010.11Data Swap1010.12Software Interrupt and Exception Entry1010.13Coprocessor Data Operation1010.14Coprocessor Data Transfer (Memory to Coprocessor)1010.15Coprocessor Data Transfer (from Coprocessor to<br>Memory)1010.16Coprocessor Register Transfer (Load from Coprocessor)1010.17Coprocessor Register Transfer (Store to Coprocessor)1010.18Undefined Instructions and Coprocessor Absent1010.19Unexecuted Instructions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            | 10.1   | Introduction                                          | 10-2  |  |

| 10.4Branch and Exchange (BX)110.5Data Operations110.6Multiply and Multiply Accumulate110.7Load Register110.8Store Register1010.9Load Multiple Registers1010.10Store Multiple Registers1010.11Data Swap1010.12Software Interrupt and Exception Entry1010.13Coprocessor Data Operation1010.14Coprocessor Data Transfer (Memory to Coprocessor)1010.15Coprocessor Data Transfer (from Coprocessor)1010.16Coprocessor Register Transfer (Load from Coprocessor)1010.17Coprocessor Register Transfer (Store to Coprocessor)1010.18Undefined Instructions and Coprocessor Absent1010.19Unexecuted Instructions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | 10.2   | Branch and Branch with Link                           | 10-2  |  |

| 10.5Data Operations110.6Multiply and Multiply Accumulate110.7Load Register110.8Store Register1010.9Load Multiple Registers1010.10Store Multiple Registers1010.11Data Swap1010.12Software Interrupt and Exception Entry1010.13Coprocessor Data Operation1010.14Coprocessor Data Transfer (Memory to Coprocessor)1010.15Coprocessor Data Transfer (from Coprocessor to<br>Memory)1010.16Coprocessor Register Transfer (Load from Coprocessor)1010.17Coprocessor Register Transfer (Store to Coprocessor)1010.18Undefined Instructions and Coprocessor Absent1010.19Unexecuted Instructions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | 10.3   | THUMB Branch with Link                                | 10-3  |  |

| 10.6Multiply and Multiply Accumulate110.7Load Register110.8Store Register1010.9Load Multiple Registers1010.10Store Multiple Registers1010.11Data Swap1010.12Software Interrupt and Exception Entry1010.13Coprocessor Data Operation1010.14Coprocessor Data Transfer (Memory to Coprocessor)1010.15Coprocessor Data Transfer (from Coprocessor to<br>Memory)1010.16Coprocessor Register Transfer (Load from Coprocessor)1010.17Coprocessor Register Transfer (Store to Coprocessor)1010.18Undefined Instructions and Coprocessor Absent1010.19Unexecuted Instructions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            | 10.4   | Branch and Exchange (BX)                              | 10-4  |  |

| 10.7Load Register110.8Store Register1010.9Load Multiple Registers1010.10Store Multiple Registers1010.11Data Swap1010.12Software Interrupt and Exception Entry1010.13Coprocessor Data Operation1010.14Coprocessor Data Transfer (Memory to Coprocessor)1010.15Coprocessor Data Transfer (from Coprocessor)1010.16Coprocessor Register Transfer (Load from Coprocessor)1010.17Coprocessor Register Transfer (Store to Coprocessor)1010.18Undefined Instructions and Coprocessor Absent1010.19Unexecuted Instructions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            | 10.5   | Data Operations                                       | 10-5  |  |

| 10.8Store Register1010.9Load Multiple Registers1010.10Store Multiple Registers1010.11Data Swap1010.12Software Interrupt and Exception Entry1010.13Coprocessor Data Operation1010.14Coprocessor Data Transfer (Memory to Coprocessor)1010.15Coprocessor Data Transfer (from Coprocessor to<br>Memory)1010.16Coprocessor Register Transfer (Load from Coprocessor)1010.17Coprocessor Register Transfer (Store to Coprocessor)1010.18Undefined Instructions and Coprocessor Absent1010.19Unexecuted Instructions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | 10.6   | Multiply and Multiply Accumulate                      | 10-7  |  |

| 10.9Load Multiple Registers1010.10Store Multiple Registers1010.11Data Swap1010.12Software Interrupt and Exception Entry1010.13Coprocessor Data Operation1010.14Coprocessor Data Transfer (Memory to Coprocessor)1010.15Coprocessor Data Transfer (from Coprocessor to<br>Memory)1010.16Coprocessor Register Transfer (Load from Coprocessor)1010.17Coprocessor Register Transfer (Store to Coprocessor)1010.18Undefined Instructions and Coprocessor Absent1010.19Unexecuted Instructions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            | 10.7   | Load Register                                         | 10-9  |  |

| 10.10Store Multiple Registers1010.11Data Swap1010.12Software Interrupt and Exception Entry1010.13Coprocessor Data Operation1010.14Coprocessor Data Transfer (Memory to Coprocessor)1010.15Coprocessor Data Transfer (from Coprocessor to<br>Memory)1010.16Coprocessor Register Transfer (Load from Coprocessor)1010.17Coprocessor Register Transfer (Store to Coprocessor)1010.18Undefined Instructions and Coprocessor Absent1010.19Unexecuted Instructions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            | 10.8   | Store Register                                        | 10-10 |  |

| 10.11Data Swap1010.12Software Interrupt and Exception Entry1010.13Coprocessor Data Operation1010.14Coprocessor Data Transfer (Memory to Coprocessor)1010.15Coprocessor Data Transfer (from Coprocessor to<br>Memory)1010.16Coprocessor Register Transfer (Load from Coprocessor)1010.17Coprocessor Register Transfer (Store to Coprocessor)1010.18Undefined Instructions and Coprocessor Absent1010.19Unexecuted Instructions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | 10.9   | Load Multiple Registers                               | 10-10 |  |

| 10.12Software Interrupt and Exception Entry1010.13Coprocessor Data Operation1010.14Coprocessor Data Transfer (Memory to Coprocessor)1010.15Coprocessor Data Transfer (from Coprocessor to<br>Memory)1010.16Coprocessor Register Transfer (Load from Coprocessor)1010.17Coprocessor Register Transfer (Store to Coprocessor)1010.18Undefined Instructions and Coprocessor Absent1010.19Unexecuted Instructions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | 10.10  | Store Multiple Registers                              | 10-12 |  |

| 10.13Coprocessor Data Operation1010.14Coprocessor Data Transfer (Memory to Coprocessor)1010.15Coprocessor Data Transfer (from Coprocessor to<br>Memory)1010.16Coprocessor Register Transfer (Load from Coprocessor)1010.17Coprocessor Register Transfer (Store to Coprocessor)1010.18Undefined Instructions and Coprocessor Absent1010.19Unexecuted Instructions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            | 10.11  | Data Swap                                             | 10-13 |  |

| 10.14Coprocessor Data Transfer (Memory to Coprocessor)1010.15Coprocessor Data Transfer (from Coprocessor to<br>Memory)1010.16Coprocessor Register Transfer (Load from Coprocessor)1010.17Coprocessor Register Transfer (Store to Coprocessor)1010.18Undefined Instructions and Coprocessor Absent1010.19Unexecuted Instructions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            | 10.12  | Software Interrupt and Exception Entry                | 10-14 |  |

| 10.15Coprocessor Data Transfer (from Coprocessor to<br>Memory)10.15Coprocessor Register Transfer (Load from Coprocessor)10.16Coprocessor Register Transfer (Load from Coprocessor)10.17Coprocessor Register Transfer (Store to Coprocessor)10.18Undefined Instructions and Coprocessor Absent10.19Unexecuted Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            | 10.13  | Coprocessor Data Operation                            | 10-15 |  |

| Memory)1010.16Coprocessor Register Transfer (Load from Coprocessor)1010.17Coprocessor Register Transfer (Store to Coprocessor)1010.18Undefined Instructions and Coprocessor Absent1010.19Unexecuted Instructions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            | 10.14  | Coprocessor Data Transfer (Memory to Coprocessor)     | 10-16 |  |

| 10.16Coprocessor Register Transfer (Load from Coprocessor)1010.17Coprocessor Register Transfer (Store to Coprocessor)1010.18Undefined Instructions and Coprocessor Absent1010.19Unexecuted Instructions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            | 10.15  | Coprocessor Data Transfer (from Coprocessor to        |       |  |

| 10.17 Coprocessor Register Transfer (Store to Coprocessor)1010.18 Undefined Instructions and Coprocessor Absent1010.19 Unexecuted Instructions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |        | Memory)                                               | 10-18 |  |

| 10.18 Undefined Instructions and Coprocessor Absent1010.19 Unexecuted Instructions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            | 10.16  | Coprocessor Register Transfer (Load from Coprocessor) | 10-20 |  |

| 10.19 Unexecuted Instructions 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | 10.17  | Coprocessor Register Transfer (Store to Coprocessor)  | 10-21 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | 10.18  | Undefined Instructions and Coprocessor Absent         | 10-22 |  |

| 10.20 Instruction Speed Summary 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            | 10.19  | Unexecuted Instructions                               | 10-23 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | 10.20  | Instruction Speed Summary                             | 10-23 |  |

| Chapter 11 | Production Test |                                                           |      |  |  |

|------------|-----------------|-----------------------------------------------------------|------|--|--|

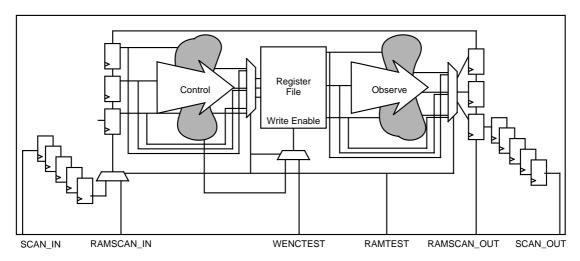

|            | 11.1            | Core Testing Strategy Overview                            | 11-1 |  |  |

|            | 11.2            | Scan Test Pin Definitions                                 | 11-2 |  |  |

|            | 11.3            | Full-Scan Production Testing                              | 11-2 |  |  |

|            |                 | 11.3.1 Register File Testing                              | 11-3 |  |  |

| Chapter 12 | Spec            | ifications                                                |      |  |  |

| Appendix A | ARM             | 7TDMI Changes                                             |      |  |  |

|            | Custo           | omer Feedback                                             |      |  |  |

| Figures    |                 |                                                           |      |  |  |

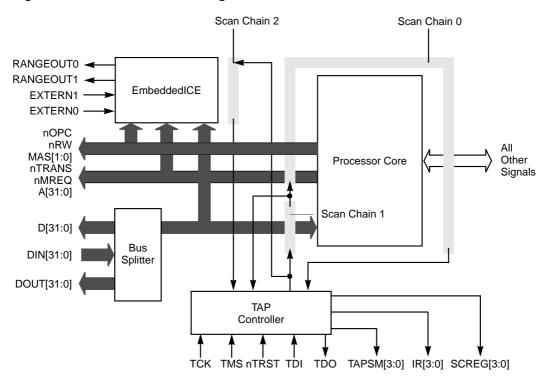

|            | 1.1             | Processor Core Diagram                                    | 1-4  |  |  |

|            | 1.2             | ARM7TDMI Core Diagram                                     | 1-5  |  |  |

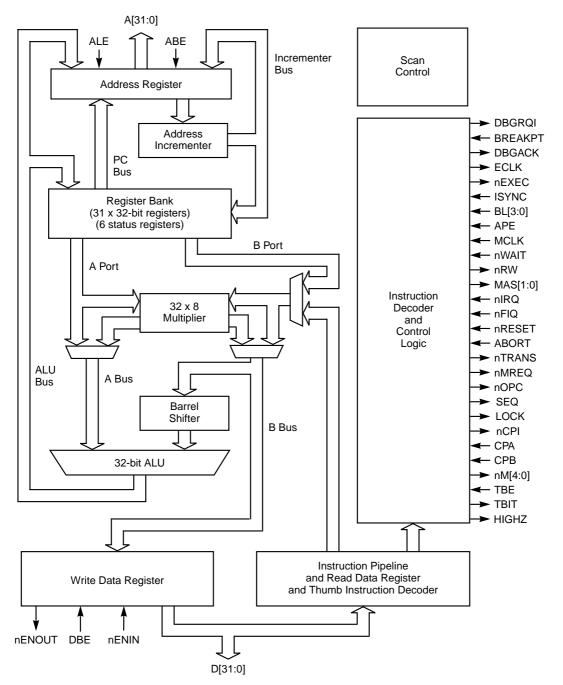

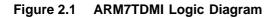

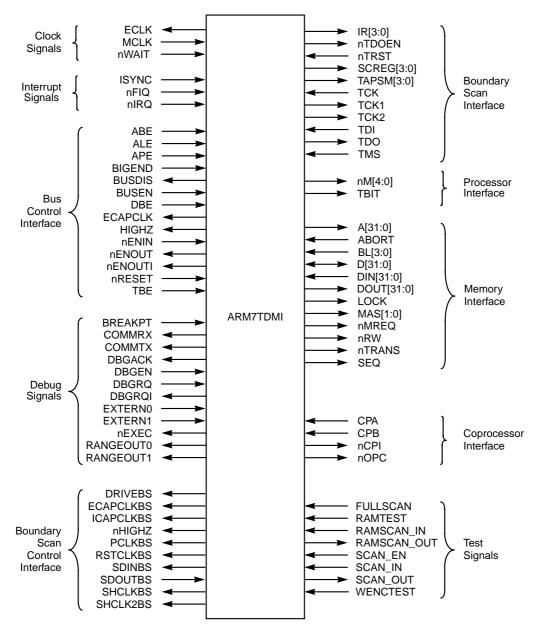

|            | 2.1             | ARM7TDMI Logic Diagram                                    | 2-2  |  |  |

|            | 3.1             | Big Endian Addresses of Bytes Within Words                | 3-3  |  |  |

|            | 3.2             | Little Endian Addresses of Bytes Within Words             | 3-3  |  |  |

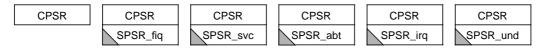

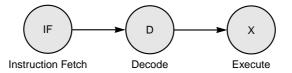

|            | 3.3             | Register Organization in ARM State                        | 3-6  |  |  |

|            | 3.4             | Register Organization in THUMB State                      | 3-7  |  |  |

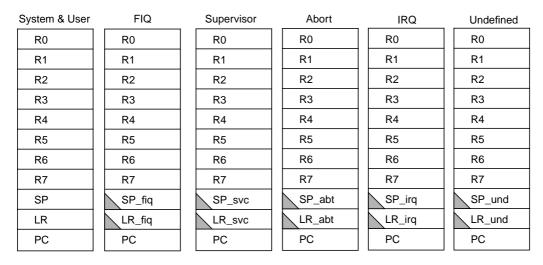

|            | 3.5             | Mapping of THUMB State Registers onto ARM State Registers | 3-8  |  |  |

|            | 3.6             | Program Status Register Format                            | 3-9  |  |  |

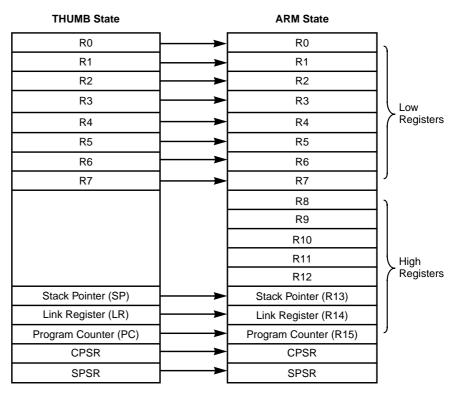

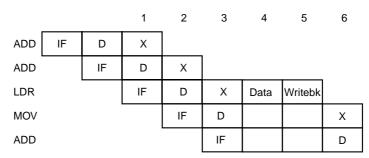

|            | 3.7             | ARM7TDMI Pipeline                                         | 3-18 |  |  |

|            | 3.8             | Pipeline Best Case Example                                | 3-19 |  |  |

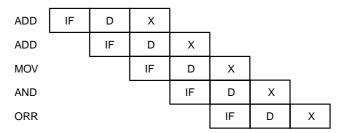

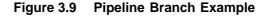

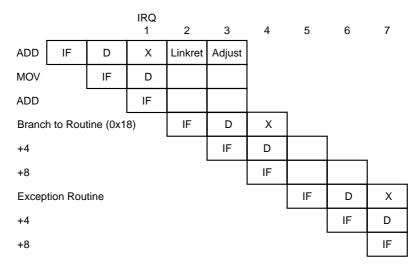

|            | 3.9             | Pipeline Branch Example                                   | 3-20 |  |  |

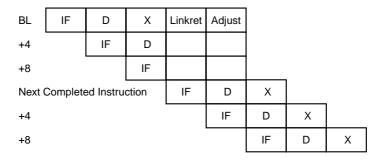

|            | 3.10            | Pipeline Interrupt Example                                | 3-21 |  |  |

|            | 3.11            | Pipeline Data Memory Access Example                       | 3-22 |  |  |

|            | 4.1             | ARM Instruction Set Formats                               | 4-3  |  |  |

|            | 5.1             | THUMB Instruction Set Formats                             | 5-4  |  |  |

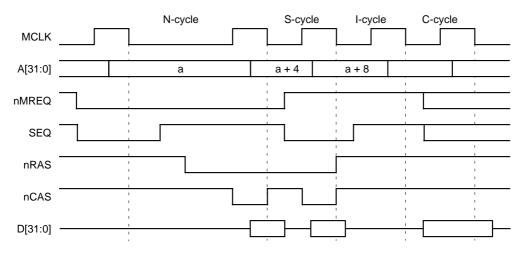

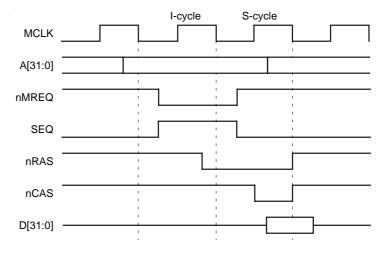

|            | 6.1             | ARM Memory Cycle Timing                                   | 6-3  |  |  |

|            | 6.2             | Memory Cycle Optimization                                 | 6-4  |  |  |

|            | 6.3             | ARM7TDMI Depipelined Addresses                            | 6-5  |  |  |

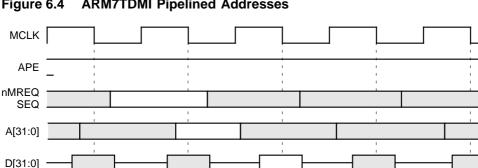

|            | 6.4             | ARM7TDMI Pipelined Addresses                              | 6-5  |  |  |

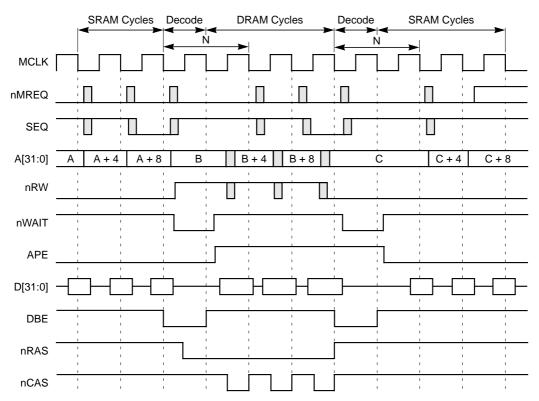

|            | 6.5             | Typical System Timing                                     | 6-6  |  |  |

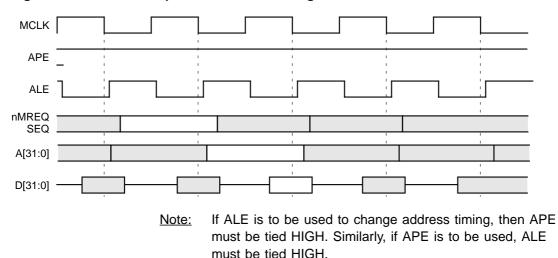

| 6.6  | SRAM Compatible Address Timing                      | 6-7  |

|------|-----------------------------------------------------|------|

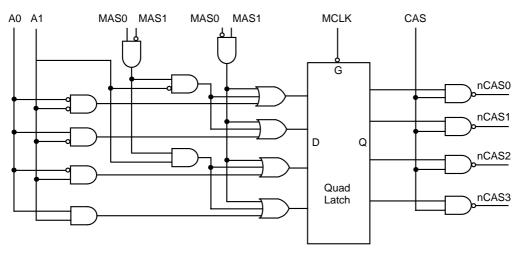

| 6.7  | Decoding Byte Accesses to Memory                    | 6-9  |

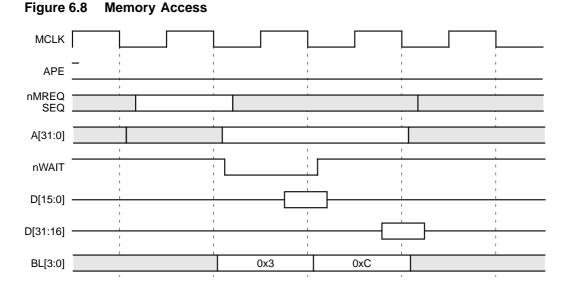

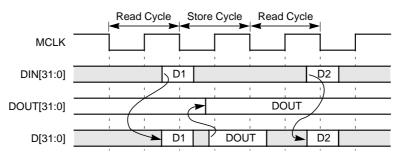

| 6.8  | Memory Access                                       | 6-12 |

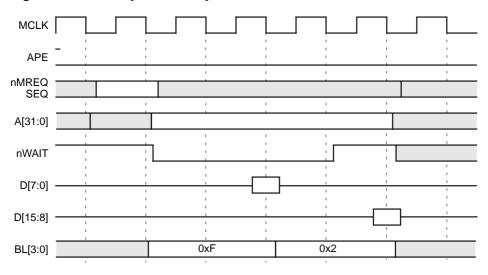

| 6.9  | Two Cycle Memory Access                             | 6-13 |

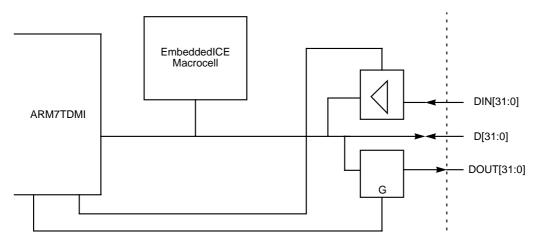

| 6.10 | ARM7TDMI External Bus Arrangement                   | 6-13 |

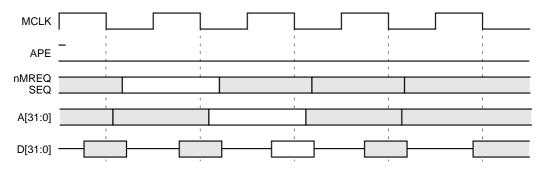

| 6.11 | Bidirectional Bus Timing                            | 6-14 |

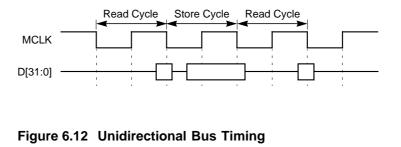

| 6.12 | Unidirectional Bus Timing                           | 6-14 |

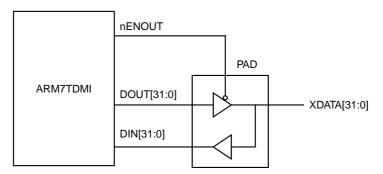

| 6.13 | External Connection of Unidirectional Buses         | 6-15 |

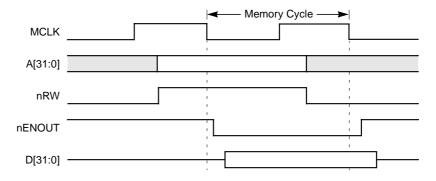

| 6.14 | Data Write Bus Cycle                                | 6-16 |

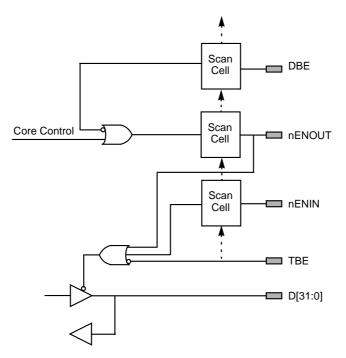

| 6.15 | ARM7TDMI Data Bus Control Circuit                   | 6-18 |

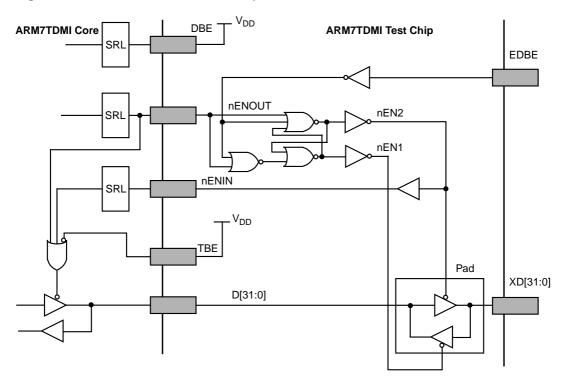

| 6.16 | The ARM7TDMI Test Chip Data Bus Circuit             | 6-19 |

| 6.17 | Data Bus Control Signal Timing                      | 6-20 |

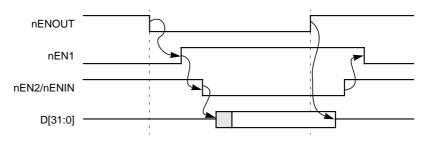

| 8.1  | Typical Debug System                                | 8-3  |

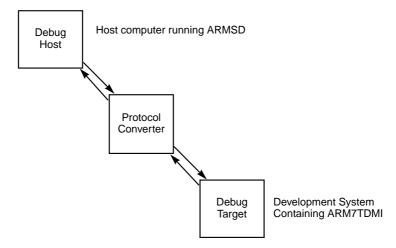

| 8.2  | Debug State Entry                                   | 8-5  |

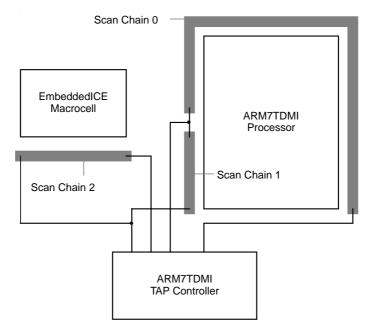

| 8.3  | ARM7TDMI Scan Chain Arrangement                     | 8-9  |

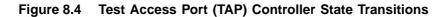

| 8.4  | Test Access Port (TAP) Controller State Transitions | 8-10 |

| 8.5  | ID Register Format                                  | 8-17 |

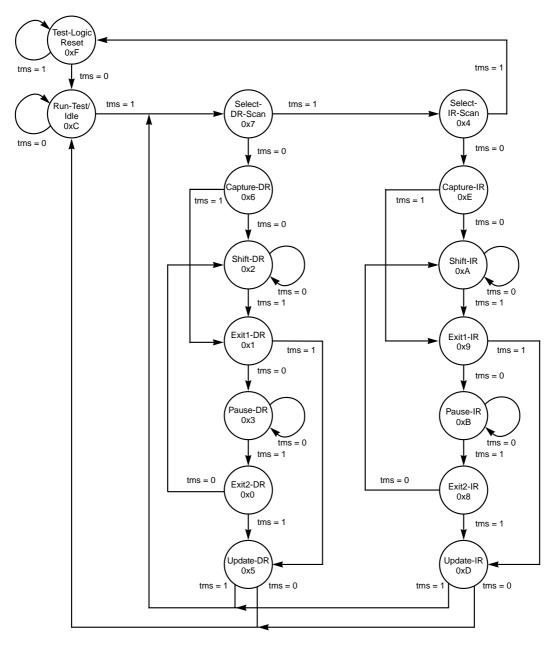

| 8.6  | Input Scan Cell                                     | 8-20 |

| 8.7  | Clock Switching on Entry to Debug State             | 8-24 |

| 8.8  | Debug Exit Sequence                                 | 8-29 |

| 8.9  | Scan General Timing                                 | 8-34 |

| 9.1  | EmbeddedICE Block Diagram                           | 9-2  |

| 9.2  | EmbeddedICE Macrocell Block Diagram                 | 9-5  |

| 9.3  | Watchpoint Control Value and Mask Format            | 9-6  |

| 9.4  | Debug Control Register Format                       | 9-11 |

| 9.5  | Debug Status Register Format                        | 9-12 |

| 9.6  | Structure of TBIT, nMREQ, DBGACK, DBGRQ and         |      |

|      | INTDIS Bits                                         | 9-14 |

| 9.7  | Debug Communications Control Register               | 9-18 |

| 11.1 | Register File Testing Scan Path                     | 11-3 |

### Tables

| 3.1   | Mode Bit States                                       | 3-11  |

|-------|-------------------------------------------------------|-------|

| 3.2   | Exception Entry/Exit                                  | 3-13  |

| 3.3   | Exception Vectors                                     | 3-16  |

| 4.1   | ARM Instruction Set                                   | 4-1   |

| 4.2   | Condition Code Summary                                | 4-5   |

| 5.1   | THUMB Instruction Set                                 | 5-1   |

| 6.1   | Memory Cycle Types                                    | 6-3   |

| 6.2   | Endian Configuration Effect on Instruction Position   | 6-9   |

| 6.3   | Output Enable Control Summary                         | 6-17  |

| 8.1   | Public Instructions                                   | 8-12  |

| 8.2   | Scan Chain Number Allocation                          | 8-19  |

| 8.3   | ARM7TDMI Scan Interface Timing                        | 8-35  |

| 8.4   | Scan Chain 0 Signal Order                             | 8-36  |

| 8.5   | ARM7TDMI Debug Interface Timing                       | 8-38  |

| 9.1   | Function and Mapping of EmbeddedICE                   |       |

|       | Registers                                             | 9-3   |

| 9.2   | IFEN Signal Control                                   | 9-12  |

| 10.1  | Branch Instruction Cycle Operations                   | 10-3  |

| 10.2  | THUMB Long Branch with Link                           | 10-4  |

| 10.3  | Branch and Exchange Instruction Cycle Operations      | 10-5  |

| 10.4  | Data Operation Instruction Cycle Operations           | 10-6  |

| 10.5  | Multiply Instruction Cycle Operations                 | 10-7  |

| 10.6  | Multiply Accumulate Instruction Cycle                 |       |

|       | Operations                                            | 10-7  |

| 10.7  | Multiply Long Instruction Cycle Operation             | 10-8  |

| 10.8  | Multiply Accumulate Long Instruction Cycle Operation  | 10-8  |

| 10.9  | Load Register Instruction Cycle Operations            | 10-9  |

| 10.10 | Store Register Instruction Cycle Operations           | 10-10 |

| 10.11 | Load Multiple Registers Instruction Cycle Operations  | 10-11 |

| 10.12 | Store Multiple Registers Instruction Cycle Operations | 10-12 |

| 10.13 | Data Swap Instruction Cycle Operations                | 10-14 |

| 10.14 | Software Interrupt Instruction Cycle Operations       | 10-15 |

| 10.15 | Coprocessor Data Operation Instruction Cycle          |       |

|       | Operations                                            | 10-16 |

| 10.16 | Coprocessor Data Transfer Instruction Cycle           |       |

|       | Operations                                            | 10-17 |

| 10.17 | Coprocessor Data Transfer Instruction Cycle           |       |

|-------|-------------------------------------------------------|-------|

|       | Operations                                            | 10-19 |

| 10.18 | Coprocessor Register Transfer (Load from Coprocessor) | 10-21 |

| 10.19 | Coprocessor Register Transfer (Store to Coprocessor)  | 10-22 |

| 10.20 | Undefined Instruction Cycle Operations                | 10-23 |

| 10.21 | Unexecuted Instruction Cycle Operations               | 10-23 |

| 10.22 | ARM Instruction Speed Summary                         | 10-24 |

| 11.1  | Scan Test Pins                                        | 11-2  |

|       |                                                       |       |

### Preface

This book is the primary reference and technical manual for the ARM7TDMI microprocessor core and contains a complete functional description for the core. The information in this manual applies to all process revisions of the core. Specific technology-dependent values, such as electrical timing, can be found in the appropriate *ARM7TDMI Microprocessor Core Datasheet*, which is available from LSI Logic.

### Audience

This document was prepared for logic designers and applications engineers and is intended to provide an overview of LSI Logic's FlexStream<sup>™</sup> system and to explain how to use the FlexStream software in the initial stages of chip design.

This document assumes that you have some familiarity with microprocessors and related support devices. The people who benefit the most from this book are:

- Engineers and managers who are evaluating the processor for possible use in a system

- Engineers who are designing the processor into a system

### Organization

This document has the following chapters and appendixes:

- Chapter 1, Introduction

- Chapter 2, Signal Descriptions

- Chapter 3, Programmer's Model

- Chapter 4, ARM Instruction Set Summary

- Chapter 5, THUMB Instruction Set Summary

- Chapter 6, Memory Interface

- Chapter 7, Coprocessor Interface

- Chapter 8, Debug Interface

- Chapter 9, EmbeddedICE Macrocell

- Chapter 10, Instruction Cycle Operations

- Chapter 11, Production Test

- Chapter 12, Specifications, see CW001007 ARM7TDMI Microprocessor Core Datasheet

- Appendix A, **ARM7TDMI Changes**

### **Related Publications**

*ARM7TDMI Data Sheet,* available from Advanced RISC Machines Ltd. as document No. ARM DDI 0029E

*CW001004 ARM7TDMI Microprocessor Core Datasheet*, available from LSI Logic.

*CW001007 ARM7TDMI Microprocessor Core Datasheet*, available from LSI Logic.

Standard Test Access Port and Boundary-Scan Architecture, IEEE Standard 1149.1 - 1990.

ARM Architectural Reference Manual, Advanced RISC Machines Ltd and Prentice-Hall.

### **Conventions Used in This Manual**

The first time a word or phrase is defined in this manual, it is *italicized*.

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive.

Hexadecimal numbers are indicated by the prefix "0x" —for example, 0x32CF. Binary numbers are indicated by the prefix "0b" —for example, 0b0011.0010.1100.1111.

Signal names are shown in capital letters.

Active LOW signals are indicated by the prefix "n" —for example, nRESET.

The manual refers to a 32-bit quantity as a *word*, a 16-bit value as a *halfword*, and an 8-bit quantity as a *byte*.

| Document Version | Release Date  | Comments                                                                                                                                                                                   |

|------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance          | December 1996 | Initial release.                                                                                                                                                                           |

| Preliminary      | January 1998  | This document was derived from the ARM document <i>ARM7TDMI Data Sheet</i> . Appendix A, <b>ARM7TDMI Changes</b> contains a list of the differences between LSI Logic and ARM's documents. |

| Final            | November 1998 |                                                                                                                                                                                            |

### Chapter 1 Introduction

This chapter introduces the core architecture, and shows block, core, and functional diagrams. It contains the following sections:

- Section 1.1, "Introduction," page 1-1

- Section 1.2, "ARM7TDMI Architecture," page 1-2

- Section 1.3, "CoreWare® Program," page 1-6

### 1.1 Introduction

This section introduces the overall core capabilities and highlights the beneficial features of LSI Logic's ARM7TDMI core implementation.

### 1.1.1 General Information

The ARM7TDMI architecture is a member of the Advanced RISC Machines (ARM) family of general purpose 32-bit microprocessors, which offer high performance for very low power consumption and price.

The ARM<sup>®</sup> architecture is based on Reduced Instruction Set Computer (RISC) principles, and the instruction set and related decode mechanism are much simpler than those of microprogrammed Complex Instruction Set Computers. This simplicity results in a high instruction throughput and impressive real time interrupt response from a small and cost effective chip.

Pipelining is employed so that all parts of the processing and memory systems can operate continuously. Typically, while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory.

The ARM memory interface has been designed to allow the performance potential to be realized without incurring high costs in the memory system. Speed critical control signals are pipelined to allow system control functions to be implemented in standard low-power logic, and these control signals facilitate the exploitation of the fast local access modes offered by industry-standard dynamic RAMs.

### 1.1.2 LSI Logic's ARM7TDMI Implementation

The ARM7TDMI Microprocessor Core described in this manual is LSI Logic's proprietary version of the ARM7TDMI microcontroller. LSI Logic's implementation represents the world's first synthesizable version of the ARM7TDMI. LSI Logic has further optimized this synthesizable version to facilitate implementation of complex system-ona-chip ASICs in LSI Logic's state-of-the-art ASIC flows.

The ARM7TDMI RTL (register-transfer level) version was developed in close conjunction with ARM, Ltd. ensuring 100% compatibility with the ARM7TDMI specification. LSI Logic's core has identical functionality and external interfaces making both the hardware and software 100% compatible with the full custom cores presently available from all other ARM7TDMI licensees. LSI Logic's RTL has been designed with single phase clocking and simplified register schemes wherever possible. This greatly eases synthesis and timing analysis of the surrounding logic and thereby facilitates the design of high-quality products with a minimum time-to-market. The RTL has been synthesized and taken through place, route, and test insertion resulting in a hardmacro ready for a system-on-a-chip design. Full scan test insertion provides high fault coverage while keeping test costs to a minimum. Finally, to implement full scan, LSI Logic has added eight additional test signals to the core (for a full description of these signals, see Chapter 2, "Signal Descriptions.")

### 1.2 ARM7TDMI Architecture

The ARM7TDMI processor employs a unique architectural strategy known as *THUMB*, which makes it ideally suited to high volume applications with memory restrictions, or applications where code density is an issue.

### 1.2.1 The THUMB Concept